# LOW COST THIN FILM SILICON SOLAR CELLS ON UPGRADED METALLURGICAL (UMG) SILICON SUBSTRATES PREPARED BY LIQUID PHASE EPITAXY (LPE)

J. Hötzel, R. Kopecek, S. Volz, K. Peter, P. Fath, E. Bucher C. Zahedi\*, F. Ferrazza<sup>+</sup> *E-mail: jochen.hoetzel@uni-konstanz.de*

Universiät Konstanz, Fachbereich Physik, Fach X916, 78457 Konstanz, Germany Tel.: +49-7531-88-3644, Fax: +49-7531-88-3895

\*Elkem ASA, Silicon Division, P.O. Box 5211 Majorstua, N-0303 Oslo, Norway <sup>+</sup>Eurosolare, Via Augusto D'Andrea 6, I-00048 Nettuno, Italy

ABSTRACT: Liquid Phase Epitaxy (LPE) was used to grow high quality thin p-type silicon films with a doping level of  $5x10^{16}$  cm<sup>-3</sup> on upgraded metallurgical (UMG) Si substrates. A melt back step prior to the growing removed the oxide, smoothed out the surface and circumvented the addition of electronic grade Si to the solution. With a steady state method the growth rates were < 0.5 µm/min. Higher rates were achieved by ramping down the temperature. The crystal structure and the electronic quality of the Si film strongly depended on the growth rate. The pn-junction was realized by a low cost P diffusion. Hydrogen passivation was quite effective and resulted in an increase in the efficiency of up to 60% relative. Contact formation was performed by both screenprinting and evaporation of Ti/Pd/Ag and Al respectively. The solar cells were analysed by I/V measurements, LBIC, SEM and spectral response data. Cells with evaporated contacts reached fill factors up to 74.1%, a V<sub>OC</sub> of 551 mV and a I<sub>SC</sub> of 14.7 mA/cm<sup>2</sup>. Therefore an efficiency of 6.0% could be achieved without antireflection coating (ARC) ( $\eta$  = 8.3% with ARC). Cells based completely on a low cost process (emitter diffusion and contacts) resulted in efficiencies of 6.6% without and 9.0% with ARC.

Keywords: Si-Films - 1: Metallurgical Grade - 2: Epitaxy - 3

# **1 OBJECTIVES**

In the last few years PV industry expanded very rapidly. This is mainly the result of a growing demand for clean energy and not least a fact of a very friendly political situation due to the rethinking of the political decision-makers in the energy question. In consequence of this development the price for one  $W_P$  continuously dropped down.

However, solar energy is not in the stage of development were it can be a serious competitor to forms. Therefore a further conventional energy dramatically cost reduction is necessary. Since the standard modules are still fabricated with cells where the thickness of the active Si region is about 300 µm, there is a big potential in switching over to thin film technology were the active layer thickness can be up to two magnitudes smaller than in standard silicon solar cells. This change reduces the needs of high quality Si in similar amounts. Beside several techniques like chemical vapour deposition (CVD), the liquid phase epitaxy (LPE) combines many favourable advantages. Apart from the fact that LPE is a low temperature method, precise doping and sharp transitions between the doped regions are possible. This technique enables to grow thin Si films of high quality on low cost Si substrates and is therefore a promising candidate to reduce the silicon feedstock problem. The compatibility of LPE to existing industrial process lines is an advantage too.

The major interest was concentrated on the realization of a LPE thin film Si solar based on a low cost substrate. The influence of the diffusion of impurities out of the substrate in the active layer and the incorporation of impurities during the growth process out of the melt was further part of our investigations. Additionally the solar cell production should be carried out by low cost methods. The substrate for the LPE was cast and sawed like conventional multicrystalline Si wafers with UMG silicon powder as the source material which is a new low cost material developed at Elkem. Thin p-type Si layers were deposited on the UMG substrate from which low cost Si solar cells with efficiencies up to 9.0% have been manufactured.

# 2 LPE GROWTH PROCESS AND EXPERIMENTAL SETUP

# 2.1 The LPE furnace

The epi layers were deposited on the UMG substrate in the LPE apparatus described in [1]. The main part of the LPE apparatus consists of a long quartz tube fixed inside a ceramic tube which is surrounded by two resistivity heated kantal wire coils. A quartz crucible in the middle of the tube is filled with indium that serves as the solvent for the silicon. The temperature is measured by two thermocouples and computer controlled. As the whole process sequence is computer controlled, the reproducibility is guaranteed to a maximum extend. A hydrogen ambient prevents the substrate from oxidation [2,3]. The hydrogen is purified by a palladium filter before flowing into the reactor. A quartz rod serves as the substrate carrier to move it into the melt. A load lock which can be evacuated and flooded with hydrogen and nitrogen enables the loading and unloading procedure.

# 2.2 LPE growth process

During the growth process the substrates were placed in a horizontal position on the surface of the melt. Layers grown from the indium solution were found to by p-type and the carrier concentration was below  $10^{16}$  cm<sup>-3</sup>. Therefore a small amount of Ga was added to the melt to obtain p-type LPE-layers in the doping range  $5 \times 10^{16}$ - $10^{17}$  cm<sup>-3</sup>. Initially the indium was saturated with silicon at 990°C. The temperature range for the growth processes was between 950°C and 990°C. To maintain the saturation of the solution with Si, a melt back step was performed prior to each growth process. Residual oxides and rough patches on the surface were removed simultaneously.

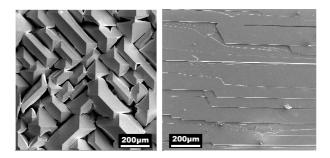

Using LPE the Si can be deposited on the substrate in different ways. The expected layer morphology is the criterion for the choice of the applied technique. To get thick, thin, smooth or rough layers depends on the growth rate which becomes the important parameter. Three techniques were used: 1) the "steady state" method, 2) the "step cooling" and 3) the "ramp cooling" method. The steady state method enables growth rates lower than 0.5 µm/min. Therefore the layer thickness was limited to 20-30 µm but the surface is very smooth (Fig. 4a). The non isotropic growth velocity which depends on the crystal orientation no longer dominates the surface morphology. Higher growth rates of 2-4 µm/min could be achieved by step cooling and by ramp cooling [4]. Here the surface morphology is differs from the previously described (Fig.4b). Each variation between a flat layer structure on (111) oriented surfaces and pyramidal growth on (100) surfaces exists on one wafer depending on the crystal orientation of the grains (Fig.2).

Figure 2: Surface morphology of LPE layers grown with a high growth rate depending on the crystal orientation of the grains. On the left the Si surface has a (100) and on the left a (111) orientation.

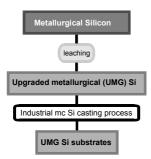

Figure 3: Industrial production process of UMG Si

# **3 UMG SI SUBSTRATE**

## 3.1 UMG Silicon

The substrate which has been used is a new low cost multicrystalline Si wafer. Metallurgical silicon was purified and leached in a special process developed at Elkem to UMG Si. For the manufacturing of wafers from the powder the standard industrial process of Eurosolare for multicrystalline Si was applied (Fig.3). Various impurities like Fe, Al, Ti or O are detectable and their proportions could be varied by changes in the leaching process.

### 3.2 Preparing of the substrates

To prepare the wafers for the growth procedure they were etched in KOH (2,5%) to remove the damage form sawing followed by a dip in HCl (5%) and rinsed in deionised water. They were dipped in HF (2%) to remove the natural surface oxides.

#### **4 DIFFUSION AND METALLISATION**

#### 4.1 Diffusion

The pn junction on the  $p^{++}/p$  substrate/LPE layer combination was realized by the diffusion of a phosphorous containing paste which was printed on the wafer by a screenprinter. After printing the wafers were dried in an infrared furnace. The firing was carried out in a belt furnace under air at temperatures between 900-960°C and the diffusion time varied between 2-20 min. Sheet resistances between 20-40  $\Omega$ sq were obtained by these diffusion parameters.

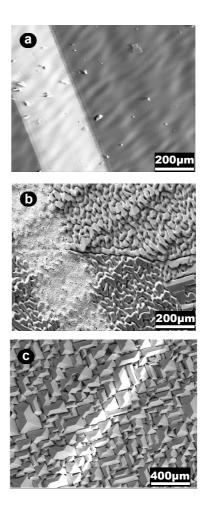

**Figure 4**: *a)* Evaporated Ti/Pd/Ag contact on a smooth LPE layer. The growth rate was  $< 0.5 \mu m/min$ , b) screenprinted finger on a rough LPE layer grown with a high growth rate (2-4  $\mu m/min$ ), c) evaporated contact on a rough surface with finger interruptions.

# 4.2 Metallisation

The metallisation of the wafers was performed by two methods: 1. Evaporation of Al for the back and Ti/Pd/Ag for the front contact. 2. Screenprinting a Ag/Al-paste for the back and a Ag paste for the front contact. Depending on the surface morphology the metallisation of the wafers was realized by evaporation and screenprinting respectively. The evaporation technique was used for flat and smooth LPE layers (Fig.4a). Wafers with a rough surface structure were contacted by screenprinting (Fig.4b). With a metal paste rough, perforated and pyramidal structures can easily be bridged over and the risk of finger interruption is very small.

# **5 HYDROGEN PASSIVATION**

One principle to improve the solar cell parameters is the elimination of defects and disturbances in crystal structure or their electrical passivation. The introduction of hydrogen is a powerful method to passivate defects like grain boundaries and dislocations especially for materials with low values of the diffusion length  $L_{diff}$  like EFG or RGS [5,6]. Since the diffusion lengths in LPE layers on UMG substrates are relatively low (10-40  $\mu$ m), we expected a significant enhancement of the cell parameters. We used a MIRHP (Microwave Induced Remote Hydrogen Plasma) passivation technique presented in [6] and adapted the process parameters to the UMG substrate/LPE-layer combination. In Fig.4 the optimal process sequence is shown:

#### 1. LPE-PROCESS

#### 2. DIFFUSION

- 3. MIRPH PASSIVATION

- 4. METALLISATION

- 5. MIRPH PASSIVATION

# 6. ANTIREFLECTION COATING

**Figure 5**: Optimal process sequence for LPE solar cells with hydrogen passivation and evaporated contacts.

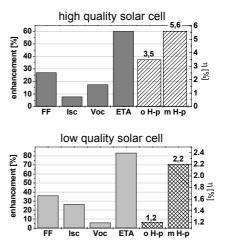

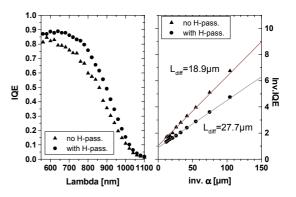

Several process sequences have been investigated. Since the behaviour of the hydrogen passsivation is additive with respect to the passivation time we gradually increased the passivation time to the point were degradation starts. It was also found that the maximum increase could be achieved with the first passivation step set before the metallisation. The optimal passivation time was found to be 210min at a temperature of 350°C. A further improvement of the sequence for screenprinted contacts could be to perform the metallisation step at the end of the process and fire the contacts through the antireflection coating. Fig. 6 shows the increase in all solar cell parameters FF,  $I_{sc}, \, V_{oc}$  and  $\eta$  after the MIRHP treatment steps 3 and 5 in Fig.5. Additionally the absolute values of  $\eta$  before and after the passivation are shown. The increase of the parameters by the passivation is the higher the lower the quality of the cell. Solar cells of high quality could be improved up to 60% relative and the profit for lower quality cells could achieve values up to 82% relative. The improvement by hydrogen passivation can be seen in the internal quantum efficiency IQE of a solar cell. In Fig.7 the IQE of a cell with and without passivation is shown on the left. On the right side the corresponding fits of the diffusion length is plotted. The higher response of the cell after the passivation is due to an increase in the diffusion length from 18.9  $\mu$ m to 27.7  $\mu$ m.

**Figure 6**: Relative gain in [%] of FF,  $V_{oc}$ ,  $J_{sc}$  and  $\eta$  after MIRHP treatment. Additionally the absolute values of  $\eta$  before (o. H-p) and after (m. H-p) passivation are shown.

Figure 7: On the left there is the IQE measurement of a cell with and without hydrogen passivation. The corresponding fits for the diffusion length is on the right.

# **6 SOLAR CELLS**

The solar cells can be split up in two groups depending on the surface morphology: 1) the smooth surface cells and 2) the rough surface cells. The first ones have high values in FF combined with low values in  $I_{SC}$ . which is characteristic for these cells. The cells of the second group stand out due to the opposite behaviour in the values for the FF and  $I_{SC}$ . The surface structure and therefore the growth rate is the important parameter as mentioned before.

For the deposition of smooth and flat layers small growth rates are necessary. The risk of holes in the epilayer down to the substrate is negligible what resulted in shunt resistances >1000  $\Omega$ cm<sup>2</sup>. On smooth surfaces front contacts can be realized easily by evaporation of Ti, Pd and Ag. The consequence of the evaporation is a high contact quality and therefore the series resistance is low which is a requirement for a high fillfactor. Additionally the risk of metal spikes through the emitter is low. But small growth rates are correlated with thin LPE-layers and therefore a relatively small value of ISC. In contrast to this rough surfaces are correlated with a high growth rate and a thicker LPE-layer. This fact and the benefits of light trapping due to the roughness resulted in high values of I<sub>SC</sub>. Rough surfaces are difficult to contact by evaporating because little steps and depressions in the surface cause interruptions (Fig.4c) or at least a decrease in the conductor cross section so that the series resistance is very high. There is also the fact that the current has to pass a longer effective way to be collected. Because the metal paste contains different ingredients the chemical reaction is not homogeneous. The paste can perform little spikes into the wafer. This combined with little variations in emitter thickness due to a rough surface can cause little contacts from the grid to the p type layer. The result is a very low shunt resistance (100-800  $\Omega cm^2)$  what finally ends in a drop down of the FF. However, to minimize the finger interruptions and therefore the series resistance screenprinted contacts on rough surfaces are necessary. The higher the growth rate the higher the density of defects and holes in the epi layer. Therefore the probability of little holes in the rough surface cells is increased, which additionally can cause low shunt resistances.

After the diffusion, the passivation and the contacting, the cells were covered with an antireflection coating. A single antireflection coating layer of  $Si_3N_4$  (ARC) was deposited by plasma enhanced chemical vapour deposition (PECVD). To achieve maximum efficiency, a double antireflection coating (DARC) was performed by the evaporation of TiO<sub>2</sub> and MgF<sub>2</sub>. Best results of LPE solar cells on low cost substrates from 1/3 UMG to pure UMG material is shown in Table 1.

**Table 1:** Parameters of different solar cells based on a low cost substrate. The substrate material varies from 1/3 UMG to pure UMG. Two cells are listed with and without ARC and DARC respectively.

| Cell (substrate)      | FF    | I <sub>SC</sub> | V <sub>OC</sub> | η   |

|-----------------------|-------|-----------------|-----------------|-----|

| LPE3 07 (1/3 UMG)     | 51.9  | 21.2            | 504             | 5.6 |

| LPE3_07 ARC (1/3 UMG) | 63.3  | 26.3            | 534             | 9.0 |

|                       |       |                 |                 |     |

| LPE6_M8c (UMG)        | 54.8  | 22.7            | 527             | 6.6 |

|                       |       |                 |                 |     |

| LPE10_10c (UMG)       | 74.06 | 14.7            | 551.11          | 6.0 |

| LPE10_10c (UMG) DARC  | 72.77 | 20.4            | 560             | 8.3 |

Comparing the samples LPE10\_10c and LPE6\_M8c it can be seen, that there is a big potential for optimisation. The high growth rate of LPE6\_M8c provides a thick layer and a high  $I_{sc}$  but the crystal quality is not as good as in LPE10\_10c. The solar cell parameters of the sample LPE10\_10c demonstrate the high crystal quality of the LPE layer. The major problem of low shunt resistances due to uncovered spots on the substrate can be avoided. The low value of  $I_{sc}$  is obviously founded on the fact of a small layer thickness and can easily be removed by growing thicker layers.

### **7 CONCLUSION**

The deposition of epitaxial layers of silicon on low cost substrates and the manufacturing of solar cells with low cost methods has been examined. A reduction in the need of high quality silicon in solar cell production by using a low cost Si substrate and the application of a thin film technology has been demonstrated. With LPE thin high quality Si layers of various morphologies has been deposited on upgraded metallurgical Si substrates. The process is nearly self-sustaining because the major Si supply to the melt is maintained by melt back the substrate before the growth process. The amount of impurities diffusing from the substrate into the LPE layer and the incorporation of impurities solved in the melt during the growth process is below the level of significant degradation. Further cost reduction could be achieved by a screenprinted emitter and screenprinted contacts. Hydrogen passivation dramatically enhanced all solar cell parameters. The solar cell results demonstrate the high quality of the LPE layers on the UMG Si substrates.

# **8 ACKNOWLEDGEMENTS**

This work was supported within the SCARF project by the European Commission under contract number JOR3-CT 97-0143-SCARF.

# **9 LITERATURE**

[1] R. Kopecek, K. Peter, J. Hötzel, E. Bucher: *Journal of Crystal Growth*, **208** (2000) 289

[2] B. J. Baliga, J. Electochem. Soc., 133, (1986) 1

[3] E. Bauser and H. P. Strunk, Mater. Res. Soc. Symp. Proc., **37**, (1991) 339

[4] J. Hötzel, K. Peter, G. Willeke, E. Bucher: 14<sup>th</sup> EC PVSEC, Barcelona, 1997, 1421

[5] P. Sana, A. Rohatgi, J. P. Kalejs, R. O. Bell: *Appl. Phys. Lett.* **64** (1), 1994, 97

[6] M. Spiegel, P. Fath, K. Peter, B. Buck, G. Willeke, E. Bucher: 13<sup>th</sup> EC PVSEC, Nizza, 1995, 421