# **REVIEW ON RIBBON SILICON TECHNIQUES FOR COST REDUCTION IN PV**

G. Hahn<sup>1</sup>, S. Seren<sup>1</sup>, M. Kaes<sup>1</sup>, A. Schönecker<sup>2</sup>, J.P. Kalejs<sup>3\*</sup>, C. Dubé<sup>4</sup>, A. Grenko<sup>5</sup>, C. Belouet<sup>6</sup>

<sup>2</sup>ECN – Solar Energy, PO Box 1, 1755 ZG Petten, Netherlands

<sup>3</sup>Schott Solar Inc., 4 Suburban Park Drive, Billerica, MA 01821, USA

<sup>4</sup>Evergreen Solar Inc., 259 Cedar Hill St., Marlboro, MA 01752, USA

<sup>5</sup>GE Energy (USA), LLC, 231 Lake Drive, Newark, DE 19702, USA

<sup>6</sup>Solarforce, 2559 Chemin Saint-André, 69760 Limonest, France

## ABSTRACT

The shortage of Si feedstock and the goal of reducing  $W_p$  costs in photovoltaics (PV) is the driving force to look for alternatives to ingot grown multicrystalline (mc) Si wafers which have the highest share in the PV market. Ribbon Si seems to be a very promising candidate as no kerf losses occur, resulting in reduced Si costs per  $W_p$ . In addition, there is no need for the energy consuming crystallization of the ingot and therefore energy payback times can be significantly reduced.

The higher defect density in ribbon Si materials has to be taken into account during cell processing, but ribbon materials already commercially available show excellent efficiencies, while for the most promising techniques efficiencies are significantly lower, but very promising.

In this presentation an overview of ribbon Si technologies currently under research will be given, based on available data on crystal growth as well as solar cell processing and cell parameters.

### INTRODUCTION

Ribbon Si wafers are a promising cost effective alternative to mc-Si wafers sliced from cast ingots as no kerf losses occur. These kerf losses together with contaminated parts near the edges of the ingot that cannot be used for cell processing add up to more than 50% of the Si starting material [1]. In addition, the current bottleneck in crystalline Si PV due to the shortage of Si feedstock increases Si prices and puts additional pressure on the fraction of wafer costs in the module.

A possible alternative to slicing wafers out of a crystallised ingot while maintaining the well proven processing techniques developed for mc-Si solar cells is the use of ribbon Si wafers. As no kerf losses occur and almost 100% of the Si feedstock ends up in the wafer material, a dramatic decrease in wafer costs is available. Apart from the better Si usage, energy costs are reduced as well, as time and energy-consuming ingot growth is eliminated. Therefore, a significantly reduced energy payback time for the PV module can be expected [2].

# **RIBBON SILICON CRYSTAL GROWTH TECHNIQUES**

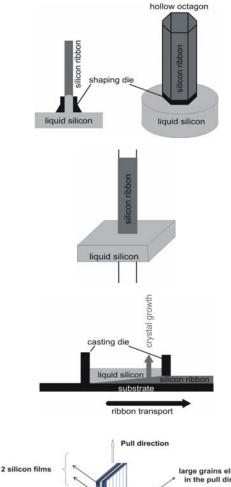

Ribbon Si crystal growth techniques can be distinguished by the shape of the meniscus that forms between the Si melt and the growing wafer [3], Fig. 1. While  $M_1$  and  $M_2$  are typical shapes for vertical ribbon growth methods, the large liquid/solid interface of  $M_3$  normally occurs for horizontal growth techniques where a supporting substrate is used.

A typical example for the  $M_1$  shape is EFG (Edgedefined Film-fed Growth) Si from Schott Solar, where the lower part of the meniscus is formed by a shaping element, a graphite die [4]. Tubes with octagon shape and facet widths of 12.5 cm can be grown.

Fig. 1: Shape of meniscus for different ribbon Si techniques.

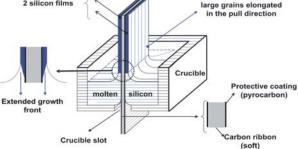

Evergreen Solar's SR (String Ribbon) with a free meniscus base on top of the molten Si is an example of the  $M_2$  geometry [5]. The advantage compared to EFG is the less restricted temperature control required near the liquid/solid interface (about 10 K instead of 1 K for EFG), which allows for a less complex furnace design. Strings that are fed through the molten Si provide edge support of the growing wafer. Throughput is lower compared to EFG as currently only two ribbons of 8 cm width are grown from one furnace (although the realisation of a four ribbon geometry is currently under investigation [6]). Both EFG and SR are already in industrial mass production.

The RGS (Ribbon Growth on Substrate) technique, currently under development at ECN, uses a substrate for support of the growing wafer and exhibits a  $M_3$  meniscus shape [7]. This geometry enables a decoupling of directions of wafer pulling and crystallisation and therefore enables very fast growth speeds. The shape of the wafer is determined by the size of the casting frame and the sub-

<sup>\*</sup> Present address: 54 Northgate Road, Wellesley, MA 02481, USA

strate that is pulled underneath the frame with the molten Si in it (current width: 10 cm with a pilot line under construction aiming for 15.6 cm).

GE Energy's MW (Molded Wafer) technique (formerly called Silicon Film) uses a substrate (width 15.6 cm) and a high growth speed (300 cm/min) [8].

The RST (Ribbon on a Sacrificial Template) technique, formerly called RAD and now again under development at Solarforce, is characterised by a vertical growth direction combined with the use of a substrate [9]. This results in a faster growth speed as compared to EFG

Fig. 2: Schematics of the ribbon Si techniques. From top to bottom: EFG, SR, RGS, RST.

and SR. Thickness of the 10 cm wide ribbon will be 200  $\mu m$  in the initial stage (5 cm/min) but is planned to be as low as 80  $\mu m$  in the future (10 cm/min).

| Table 1: Pro | perties of | ribbon | Si | arowth | technia | ues. |

|--------------|------------|--------|----|--------|---------|------|

|--------------|------------|--------|----|--------|---------|------|

|     | meniscus       | pull speed<br>[cm/min] | throughput<br>[cm <sup>2</sup> /min] |

|-----|----------------|------------------------|--------------------------------------|

| EFG | M <sub>1</sub> | 1-2                    | 136                                  |

| SR  | M <sub>2</sub> | 1-2                    | 13                                   |

| RGS | M <sub>3</sub> | 650                    | 6500 (10140)                         |

| MW  | M <sub>3</sub> | ~300                   | 4680                                 |

| RST | $M_2/M_3$      | 5 (10)                 | 100 (200)                            |

#### **DEFECTS IN RIBBON SILICON**

Due to the specific growth condition, each ribbon technique results in different defect concentrations and distributions. It can be stated that there is a trend towards smaller grain sizes with increased pulling speed. EFG wafers tend to have a high [C] due to the graphite die close to the liquid/solid interface. Both EFG and SR show a low [O], and strong efforts led to a significant reduction in [O] for RGS, which is now in the range of ingot cast mc-Si. Nevertheless, RGS still has to deal with very high [C] at the moment. MW has to deal with both high [C] and high [O], while RST has similar properties as EFG.

Table 2: Interstitial oxygen and substitutional carbon content as well as grain size for ribbon Si materials.

|     | [O <sub>i</sub> ]<br>[10 <sup>17</sup> cm <sup>-3</sup> ] | [C₅]<br>[10 <sup>17</sup> cm <sup>-3</sup> ] | grain size                       |

|-----|-----------------------------------------------------------|----------------------------------------------|----------------------------------|

| EFG | <1                                                        | 10-15                                        | cm <sup>2</sup>                  |

| SR  | <1                                                        | 5-7                                          | cm <sup>2</sup>                  |

| RGS | 3-5                                                       | 20-30                                        | <mm<sup>2</mm<sup>               |

| MW  | 2-10                                                      | 3-5                                          | mm <sup>2</sup>                  |

| RST | <1                                                        | 5                                            | mm <sup>2</sup> -cm <sup>2</sup> |

### **GETTERING AND HYDROGENATION**

To improve crystal quality and electronic properties of ribbon Si, gettering and hydrogenation techniques play a key role for reaching higher cell efficiencies [10]. They are normally part of solar cell processing in order to reduce cost while not applying additional processing steps. An exception is MW, where an annealing step is routinely carried out prior to cell processing which can significantly reduce interstitial O and substitutional C concentration in the upper part of the wafer [11], leading to fewer defects in the active area.

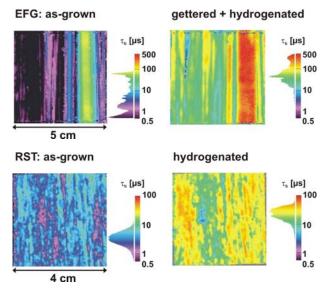

Several authors recently described gettering and hydrogenation studies in ribbon Si, especially for EFG, SR, and RGS, and strong improvements in carrier lifetimes have been observed [12-17]. Trapping of H in Si seems to be a crucial mechanism to explain the largely differing effective diffusion constant of H in Si. To a large degree this can be attributed to the O acting as a trapping centre for H, especially in precipitated form [18].

# Preprint 4<sup>th</sup> WC PEC Waikoloa 2006

Fig. 3: Minority carrier bulk lifetimes of an EFG sample in the as-grown state and after gettering and hydrogenation using PECVD  $SiN_x$  deposition plus firing, top. RST sample as-grown and after hydrogenation using microwave-induced remote hydrogen plasma (MIRHP), bottom.

The distribution of metal impurities and other defects is different in ribbon materials compared to ingot cast wafers [19]. The precipitates present in ribbons after crystallization show a tendency to be smaller and more homogenously distributed because of the faster cooling rates, giving the impurities less time for precipitation [20].

### SOLAR CELLS

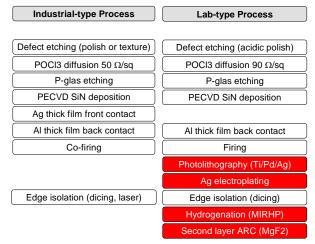

To evaluate the potential of solar cells processed from ribbon Si materials, industrial-type and lab-type cell processes (Fig. 4) have to be distinguished. While the first one demonstrates the behaviour on large wafer formats with fabrication methods suitable for mass production, the latter is used for determination of the ultimate efficiency potential of a material.

Record cell efficiencies reached on ribbon Si wafers are shown in Table 3. Listed are record values for the corresponding materials and processes, to the best of our knowledge. There are no cell data available yet for RST material. Efficiencies in the 18% range are possible using lab-type processes on EFG and SR. These cells are mainly limited by recombination at the back side, where a full Al back surface field was applied, and a lack of an effective surface texture. Record cell efficiencies for industrial-type processes for these materials are in the 16% range. One reason for this discrepancy apart from process related issues is the inhomogeneous material quality causing lower efficiencies on larger cell formats.

Lab-type processing for RGS and MW using current material quality results in efficiencies in the 13-14% range, mainly limited by diffusion lengths of ~100 µm. Industrial cell processing leads to efficiencies of about 12-13%.

Fig. 4: Examples for an industrial (left) and a lab-type photolithography based cell process (right).

While EFG and SR are already comparable with standard ingot cast mc-Si efficiencies, RGS and MW still have to be improved in quality to reach higher efficiencies. If this can be achieved, a significant cost reduction in PV is possible, as the throughput of these materials is so high.

The application of a surface texture for minimizing optical losses is another issue to be addressed in the future. Due to the shiny surface of EFG and SR material without any surface damage, standard alkaline or acidic textures do not work well. Up to now there are no reports of increased cell efficiency for textured EFG or SR. RGS and MW material behave differently, as an acidic surface texture has already been demonstrated [15, 21].

Table 3: Cell parameters of record cells for different ribbon technologies. L: lab-type, I: industrial-type process.

| Material                       | V <sub>oc</sub><br>[mV] | J <sub>sc</sub><br>[mA/cm <sup>2</sup> ] | FF<br>[%] | η<br>[%] |

|--------------------------------|-------------------------|------------------------------------------|-----------|----------|

| EFG L 4 cm <sup>2</sup> [22]   | 624                     | 36.8                                     | 79.2      | 18.2     |

| EFG I 100 cm <sup>2</sup> [23] | 603                     | 33.4                                     | 78.7      | 15.7     |

| SR L 4 cm <sup>2</sup> [22]    | 621                     | 36.7                                     | 78.6      | 17.9     |

| SR I 80 cm <sup>2</sup> [24]   | 609                     | 33.8                                     | 77.6      | 16.0     |

| RGSL4 cm <sup>2</sup>          | 587                     | 29.2                                     | 78.0      | 13.4     |

| RGS I 25 cm <sup>2</sup> [15]  | 589                     | 28.6                                     | 76.3      | 12.9     |

| MW L 4 cm <sup>2</sup>         | 570                     | 31.4                                     | 78.0      | 14.0     |

| MW I 25 cm <sup>2</sup> [21]   | 559                     | 28.5                                     | 75.0      | 11.9     |

## SI USAGE AND ENERGY PAY-BACK TIME

An interesting measure in PV today with the predicted Si shortage becoming a reality is the amount of Si feedstock that is used to generate 1  $W_p$  of power. Under the simplified assumption that 100% of the feedstock ends up in the wafers for all ribbon techniques, this  $g/W_p$  (or  $t/MW_p$ ) data can be calculated with wafer dimensions and record efficiencies for industrial-type cell process as input parameters for a rough estimate (Table 4, no efficiencies available for RST). For mc-Si an average efficiency value of 15% is assumed. A significant reduction in Si feedstock per generated  $W_p$  can be achieved when using ribbon Si techniques. For MW more impurities in the Si feedstock can be tolerated, therefore feedstock costs are significantly lower than for standard mc-Si ingot wafers as well.

Apart from lower Si feedstock consumption, avoidance of time and energy consuming ingot crystallization steps brings down wafer costs for ribbon techniques as well. This results in a significantly reduced energy payback time of the ribbon Si solar module, provided module efficiencies are high enough, as shown e.g. in [2].

Table 4: Si feedstock usage per generated W<sub>p</sub>.

: photolithography process, first test

\*\*: no standard electronic grade Si needed

| Material    | thickness [µm]   | η [%]  | g <sub>Si</sub> /₩ <sub>p</sub> |

|-------------|------------------|--------|---------------------------------|

| mc-Si ingot | ~250             | 15     | 10.5                            |

| EFG         | 300              | 16     | 4.4                             |

| SR          | 300              | 16     | 4.4                             |

| RGS         | 300 <i>(150)</i> | 13(11) | 5.4(3.2)                        |

| MW          | 600              | 12(14) | 11.7 <i>(10.1)</i> **           |

### SUMMARY

Ribbon Si technologies can be distinguished by the shape of the meniscus at the liquid/solid interface. By this approach the classical vertical growth techniques EFG and SR with lower pulling speeds (1-2 cm/min) can be separated from the horizontal growth techniques RGS and MW with higher pulling speeds (300-650 cm/min), allowing a higher throughput. RST can be classified as a mixture of these two classes.

The higher defect density in ribbon Si as compared to standard mc-Si from ingots can be addressed by optimised gettering and hydrogenation schemes. Due to the fast crystallization and varying impurity concentrations, the distribution and size of precipitates present in ribbons can differ significantly from ingot grown mc-Si material.

In EFG and SR excellent lifetimes can be reached with record cell efficiencies in the same range as for mc-Si from ingots, although some extended lower quality areas still limit cell performance [25].

For RGS and MW gettering and hydrogenation are very important process steps, too, but the higher defect density and the lower as-grown crystal quality is still limiting cell efficiencies.

The Si feedstock usage per  $W_{\rm p}$  can be reduced, and in combination with lower energy consumption during crystallization, energy payback times can be shortened. All this should lead to a significant reduction in  $W_{\rm p}$  costs.

Data published on Sharp's ribbon technique ( $M_3$  meniscus, similar to RGS) is very limited, therefore it was not included in this overview.

#### ACKNOWLEDGEMENTS

The underlying projects of parts of this report were supported with funding of the German BMU under contract number 0329846J and by the EC within the RGSells and CRYSTALCLEAR project (ENK6-CT2001-00574, SES6-CT-2003-502583). The content of this publication is the responsibility of the authors.

### LITERATURE

- D. Sarti, R. Einhaus, Solar Energy Materials & Solar Cells 72 2002 27

- [2] E.A. Alsema, M.J. de Wild-Scholten, Proc. 19<sup>th</sup> EC PVSEC, Paris 2004, 840

- [3] T.F. Ciszek, J. Crystal Growth 66 1984 655

- [4] F.W. Wald in: Crystals: Growth, Properties, and Applications 5, (Berlin: Springer 1981) 147

- [5] W.M. Sachs, D. Ely, J. Serdy, J. Crystal Growth 82 1987 117

- [6] E. Sachs, D. Harvey, R. Janoch, A. Anselmo,

D. Miller, J.I. Hanoka, *Proc. 19<sup>th</sup> EC PVSEC, Paris* 2004, 552

- [7] H. Lange, I. Schwirtlich, J. Crystal Growth 104 1990 108

- [8] J. Rand, G. Rozgonyi, J. Lu, R. Reedy, Proc. 29<sup>th</sup> IEEE PVSC, New Orleans 2002, 98

- [9] C. Belouet, J. Crystal Growth 82 1987 110

- [10] C. Dubé, J.I. Hanoka, Proc. 31<sup>st</sup> IEEE PVSC, Lake Buena Vista 2005, 883

- [11] J. Lu, G. Rozgonyi, J. Rand, R. Jonczyk, 15<sup>th</sup> NREL workshop, Vail 2005, 196

- [12] A. Rohatgi, V. Yelundur, J. Jeong, A. Ebong,

D. Meier, A.M. Gabor, M.D. Rosenblum, *Proc.* 16<sup>th</sup> EC PVSEC, Glasgow 2000, 1120

- [13] P. Geiger, G. Kragler, G. Hahn, P. Fath, Solar Energy Materials & Solar Cells 85 2005 559

- [14] M. Kaes, G. Hahn, A. Metz, Proc. 31<sup>st</sup> IEEE PVSC, Lake Buena Vista 2005, 923

- [15] A.R. Burgers, A. Gutjahr, L. Laas, A. Schönecker, S. Seren, G. Hahn, this conference

- [16] G. Hahn, A. Schönecker, J. Phys.: Condens. Matter 16 2004 R1615-R1648

- [17] M. Kaes, G. Hahn, T. Pernau, A. Metz, Proc. 20<sup>th</sup> EC PVSEC, Barcelona 2005, 1063

- [18] G. Hahn, A. Schönecker, A.R. Burgers, R. Ginige, K. Cherkaoui, D. Karg, Proc. 20<sup>th</sup> EC PVSEC, Barcelona 2005, 717

- [19] J.P. Kalejs, Solid State Phen. 95-96 2004 159

- [20] T. Buonassisi et al., *Prog. Photovolt: Res. Appl.* 2006, in press

- [21] S. Seren, G. Hahn, A. Gutjahr, A.R. Burgers, A. Schönecker, A. Grenko, R. Jonczyk, this conference

- [22] A. Rohatgi, D.S. Kim, V. Yelundur, K. Nakayashiki, A. Upadhyaya, M. Hilali, V. Meemongkolkiat, *Technical Digest* 14<sup>th</sup> PVSEC, Bangkok 2004, 635

- [23] J. Horzel, G. Grupp, R. Preu, W. Schmidt, Proc. 20<sup>th</sup> EC PVSEC, Barcelona 2005, 895

- [24] G. Hahn, A.M. Gabor, Proc. 3<sup>rd</sup> WC PVSEC, Osaka 2003, 1289

- [25] K. Nakayashiki, V. Meemongkolkiat, A. Rohatgi, IEEE Transaction on Electron Devices 52 2005 2243